SystemVerilog Dice Game Design and Verification

- A digital dice game

- Schematic-based system to SystemVerilog and verification environment

Why This Project

- A more in-depth understanding of SystemVerilog

- A realistic starting point

Final Result

- A modular SystemVerilog implementation

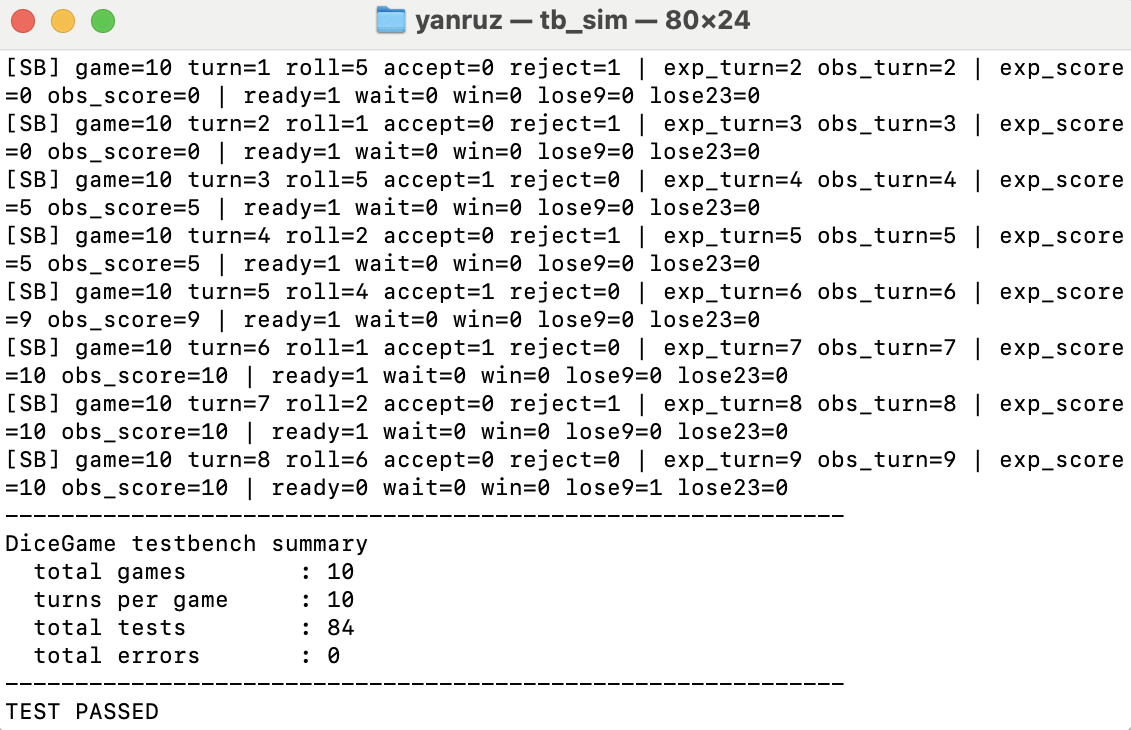

- A self-checking verification environment

From Schematic to SystemVerilog

- The original project was designed for an FPGA platform.

- The player uses buttons and switches on the board to control the game.

- You press a button to roll the dice, and the game adds that result to your score.

- If the number is not 6, you can choose whether to accept it or reject it.

- The goal is to reach a score of 23 within 9 turns.

- If your score goes over 23, or if you use up all 9 turns before reaching 23, then you lose.

Design Breakdown

Controller

The controller handles the state transitions of the game, including when the machine is

ready to roll, when it should wait for a decision, and when win or loss conditions are met.

Roll Logic

The roll logic is responsible for generating the dice result and feeding that value into the

rest of the game flow.

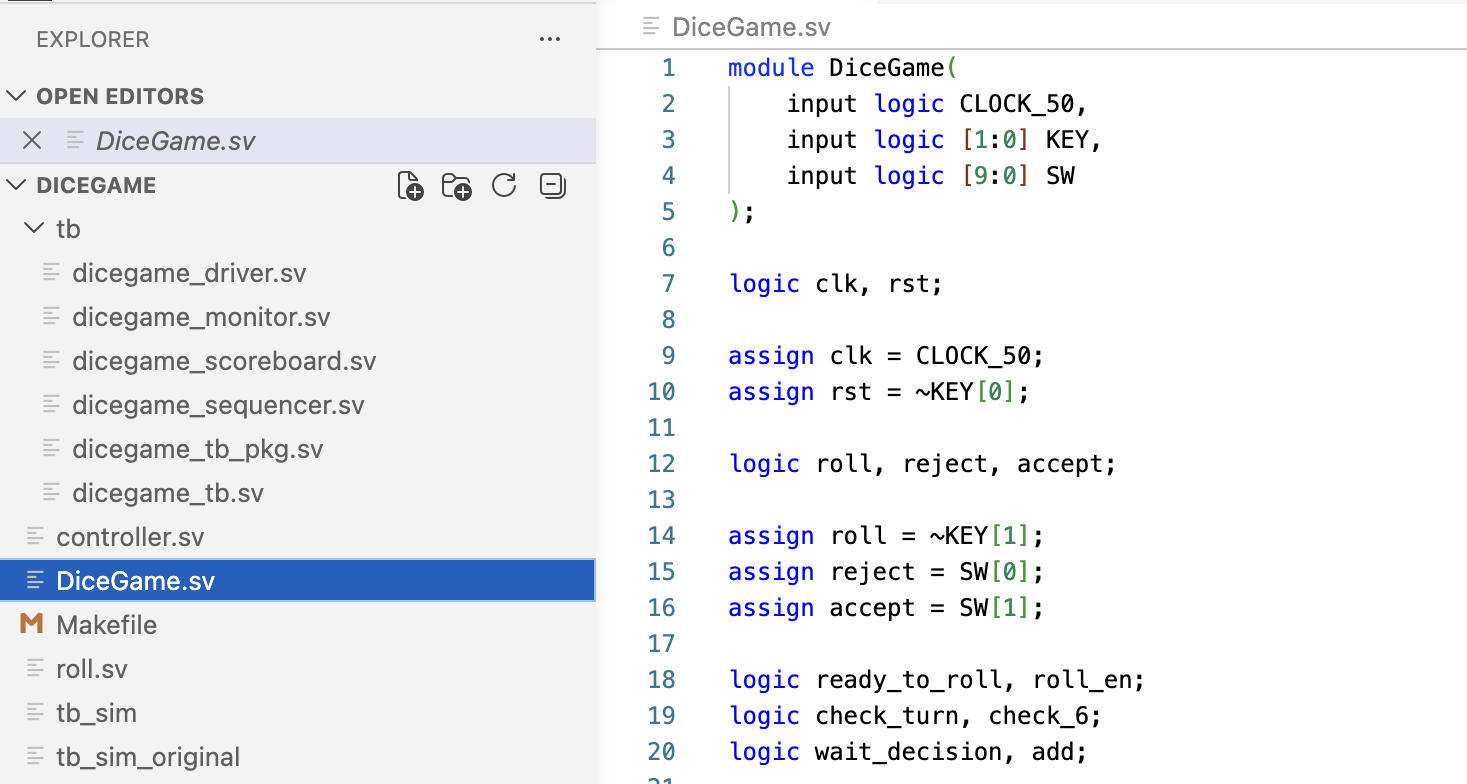

Top Level

The top-level module ties the pieces together and receives the external FPGA-style inputs

such as reset, roll, accept, and reject.

Verification Environment

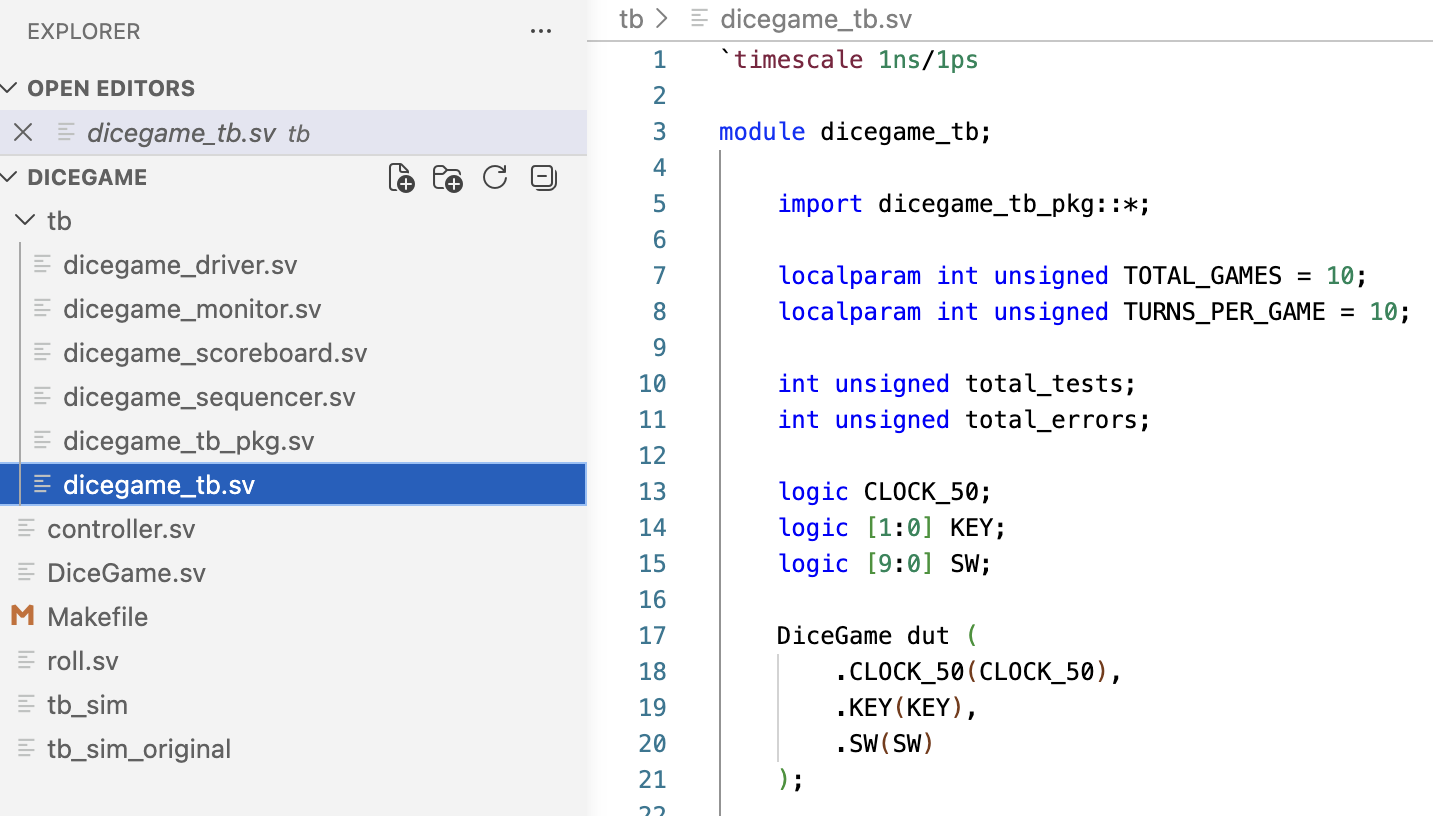

- Traditional SystemVerilog testbench structure, including a sequencer, driver, monitor, and scoreboard.

Debugging and Challenges

- Fully translate the original design into SystemVerilog

- Passing self-checking simulation

- Syntax errors

- Timing issues and state-related bugs

ECE Skills and Next Steps

- More experience with digital design

- More familiar with SystemVerilog syntax

- Practiced finite state machine design

- Using HDL to design the FSM -- more concise than schematics.

- Experience with verification

- Future improvements: Use an actual FPGA board, UVM